-KAIST 최양규 교수 공동연구팀, IoT 자율주행 등 5G/6G 해킹 보안용 암호 반도체 소자

-연구팀, 전력 소모 약 3,800배 개선 가능한 세계 유일 구조의 난수 발생기를 최초로 개발

|

| (왼쪽부터) 최양규 교수, 류승탁 교수, 김승일 박사과정. |

사물인터넷(IoT), 자율 주행 등 5G/6G 기반의 초연결성 시대에 모든 소자 및 기기 간의 정보 교환이 급증함에 따라 해킹 공격이 빈번해지고 수법 또한 고도화 되고 있다. 상호 간 데이터를 안전하게 주고받기 위해 보안이 보장되어야 하므로, 난수발생기는 모든 보안 환경에서 가장 중요한 요소이다. 이에 따라, 기기에서 데이터를 안전하게 전송하기 위해서는 보안 기능 강화가 필수적이다.

KAIST 전기및전자공학부 최양규 교수와 류승탁 교수 공동연구팀이 ‘해킹 막는 세계 최초 보안용 암호 반도체’를 개발하는 데 성공했다고 밝혔다.

연구팀은 100% 실리콘 호환 공정으로 제작된 핀펫(FinFET) 기반 보안용 암호반도체 크립토그래픽 트랜지스터(cryptographic transistor, 이하 크립토리스터(cryptoristor))를 세계 최초로 개발했다. 이는 트랜지스터 하나로 이루어진 독창적 구조를 갖고 있을 뿐만 아니라, 동작 방식 또한 독특해 유일무이한 특성을 구비한 난수발생기다.

인공지능 등의 모든 보안 환경에서 가장 중요한 요소는 난수발생기이다. 가장 널리 사용되는 보안 칩인 ‘고급 암호화 표준(advanced encryption standard, AES)’에서 난수발생기는 핵심 요소로, AES 보안 칩 전체 면적의 약 75%, 에너지 소모의 85% 이상을 차지한다. 따라서, 모바일 혹은 사물인터넷(IoT)에 탑재가 가능한 저전력/초소형 난수발생기 개발이 시급하다.

기존의 난수발생기는 전력 소모가 매우 크고 실리콘 CMOS 공정과의 호환성이 떨어진다는 단점이 있고, 회로 기반의 난수발생기들은 점유 면적이 매우 크다는 단점이 있다.

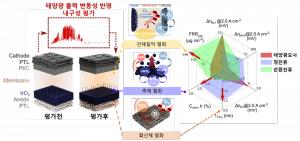

|

| 개발한 보안용 암호 반도체 소자 개념도 |

연구팀은 기존 세계 최고 수준 연구 대비 전력 소모와 점유 면적 모두 수천 배 이상 작은 암호 반도체인 단일 소자 기반의 크립토리스터(cryptoristor)를 개발했다. 절연층이 실리콘 하부에 형성되어 있는 실리콘 온 인슐레이터(Silicon-on-Insulator, SOI) 기판 위에 제작된 핀펫(FinFET)이 가지는 내재적인 전위 불안정성을 이용해 무작위적으로 0과 1을 예측 불가능하게 내보내는 난수발생기를 개발했다.

다시 설명하면, 보통 모바일 기기 등에서 정보를 교환할 때 데이터를 암호화하는 알고리즘에는 해커가 암호화한 알고리즘을 예측할 수 없도록 하는 것이 중요하다. 이에 무작위의 0과 1이 난수이며 0과 1의 배열이 매번 다른 결과가 나오게 하여 예측 불가능성을 가지도록 함으로써 공격자가 예측하지 못하도록 차단하는 방식이다.

특히, 크립토리스터 기반 난수발생기 연구는 국제적으로도 구현한 사례가 없는 세계 최초의 연구이면서, 기존 논리 연산용 또는 메모리용 소자와 동일한 구조의 트랜지스터이기 때문에, 현재 반도체 설비를 이용한 양산 공정으로 100% 제작이 가능하며 저비용으로 빠르게 대량생산이 가능하다는 점에서 의미가 크다.

연구를 주도한 KAIST 김승일 박사과정은 개발된 “암호 반도체로서 초소형/저전력 난수발생기는 특유의 예측 불가능성으로 인해 보안 기능을 강화해 칩 또는 칩 간의 통신 보안으로 안전한 초연결성을 지원할 수 있고, 특히 기존 연구 대비 에너지, 집적도, 비용 측면에서 탁월한 장점을 갖고 있어 사물인터넷(IoT) 기기 환경에 적합하다”고 연구의 의의를 설명했다.

KAIST 전기및전자공학부 김승일 박사과정이 제1 저자, 유형진 석사가 공저자로 참여한 이번 연구는 국제학술지 ‘사이언스(Science)’의 자매지인 ‘사이언스 어드밴시스(Science Advances)’ 2024년 2월 온라인판에 정식 출판됐다. (논문명 : Cryptographic transistor for true random number generator with low power consumption) 한편 이번 연구는 한국연구재단 차세대지능형반도체기술개발사업, 국가반도체연구실지원핵심기술개발사업의 지원을 받아 수행됐다.

□ 연구개요

연구 배경

난수 발생기에서 발생되는 무작위한 0과 1 출력은 정보 송수신 시 정보를 암호화 또는 복호화 하는데 사용 되어 해킹 시도를 차단한다. 난수발생기는 가장 널리 사용되는 보안 칩인 advanced encryption standard (AES)에 필요한 핵심 요소이면서 AES 보안 칩 전체 면적의 약 75%, 에너지 소모의 85% 이상을 차지한다. 따라서, 모바일 혹은 사물인터넷 (IoT)에 적용되기 위해서는 저전력/초소형 난수발생기 개발이 시급하다.

한편, 한편, 기존의 난수발생기는 단일 소자로써 resistive random access memory (RRAM) 소자 혹은 magnetic random access memory (MRAM)과 같은 신소재 기반의 소자나, 모듈로써 실리콘 CMOS 회로로 구현 하는 방법이 제안되었다. 그러나 기존의 RRAM 혹은 MRAM 기반의 난수발생기는 전력소모가 매우 크고 실리콘 CMOS 공정과의 호환성이 떨어진다는 단점이 있고, 회로 기반의 난수발생기는 점유면적이 매우 크다는 단점이 존재한다. 따라서, 모바일 IoT 환경에 적합하도록 전력 소모와 점유면적을 모두 낮춘 단일 소자 기반의 신개념 난수발생기 개발이 필요하다.

2. 연구 내용

연구팀은 SOI 기판 위에 트랜지스터를 만들어 기존 세계 최고 수준 연구 대비 전력소모와 점유면적 모두 수 천배이상 작은 보안용 암호반도체인 cryptoristor를 개발하였다. 제작된 암호반도체는 특유의 역동적 전위 불안정성으로 인한 무작위한 전압출력으로 예측 불가능한 난수를 발생시킨다. 추가적으로 암호반도체의 무작위한 아날로그 전압 출력을 0과 1의 디지털 비트로 바꿔줌과 동시에, 난수성을 향상시키는 저전력 소모형 noise-coupling analog-to-digital converter (NC-ADC)를 개발하여 저전력/고효율/초소형의 난수발생기를 구현했다. 특히, 제작된 암호반도체는 국내/국제적으로 유사 특허가 단 한 건도 없었고, 연구로도 구현한 사례가 없는 세계 최초의 시도이었다. 구조 및 동작 방식 또한 유일해, 손쉽게 독보적 암호반도체 원천기술을 확보했다. 더 나아가, 100% CMOS 공정으로 제작되어 양산에 바로 적용할 수 있다는 점에서 기술적 의미가 크다.

3. 기대 효과

연구팀이 개발한 암호반도체는 저전력과 초소형 기능이 필수적인 IoT 기기 환경에서 강력한 보안성 확보로 사용자의 정보를 보호할 수 있다. 또한, 개발한 암호반도체는 점유면적이 매우 작아 생산단가를 획기적으로 낮출 수 있어 동종분야 타 기술 대비 경쟁력이 매우 높아 보안 시장 분야를 빠르게 장악할 수 있다. 2022 IoT Analytics Research에 따르면 전세계 IoT 보안 시장은 연평균 22% 성장세를 지속해 2027년까지 5250억 달러 규모로 성장할 것으로 예상하며, 시장 선점 시 큰 경제적 파급 효과가 있을 것으로 기대된다.

노벨사이언스 science@nobelscience.co.kr